## **MODULE 4:**

**Flip-Flops** (Text-2) 5Hours: Introduction to Flip-Flops (Section 12.1), NAND Gate Latch/NOR Gate Latch, RS Flip-Flop, Gated Flip-Flops: Clocked RS Flip-Flop (Sections 12.3 to 12.5).

**Microcontrollers** (Ref.1) 5Hours: Introduction to Microcontrollers, 8051 Microcontroller Architecture and an example of Microcontroller based stepper motor control system (only Block Diagram approach).

# Flip-Flops:

A flip-flop is an electronic circuit, which stores one bit memory. The memory elements in a sequential circuit are called *flip-flops*. A flip-flop circuit has two outputs, one for the normal value and one for the complement value of the stored bit.

Binary information can enter a flip-flop in a variety of ways and gives rise to different types of flip-flops. Difference between Combinational Logic Circuits and Sequential Logic Circuits

| Sl No. | Combinational Logic Circuits                                                                                                                                                                          | Sequential Logic Circuits                                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | The simple time independent logic circuits that are implemented using Boolean circuits whose output logic value depends only on the input logic values can be called as combinational logic circuits. | The simple logic circuits whose output logic value depends on the input logic values and also on the stored information is called as sequential logic circuits |

| 2      | Thus, these combinational digital logic circuits don't have the capability to store a state inside them.                                                                                              | Sequential digital logic circuits are capable of storing the data in a digital circuit.                                                                        |

| 3      | There is no feedback path between input and output                                                                                                                                                    | There is a feedback path between input and output                                                                                                              |

| 4      | Hence, the combinational logic circuits do not contain any memory elements.                                                                                                                           | The sequential logic circuits contain memory elements.                                                                                                         |

| 5      | Examples half adder, and full adders.                                                                                                                                                                 | Flip-Flop, counters                                                                                                                                            |

| 6      | Processing Speed is fast                                                                                                                                                                              | Processing speed is less.                                                                                                                                      |

### **Introduction - Triggering of Flip-flops**

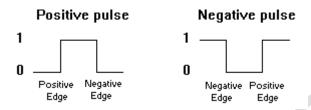

The clock pulse goes through two signal transitions: from 0 to 1 and the return from 1 to 0. As shown in figure 1, the positive transition is defined as the positive edge and the negative transition as the negative edge.

Figure 1 Clock pulse transition

The clocked flip-flops already introduced are triggered during the positive edge of the pulse, and the state transition starts as soon as the pulse reaches the logic-1 level. If the other inputs change while the clock is still 1, a new output state may occur. If the flip-flop is made to respond to the positive (or negative) edge transition only, instead of the entire pulse duration, then the multiple-transition problem can be eliminated.

## **Introduction - Basic Flip-Flop Circuit**

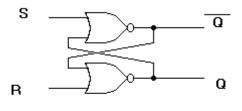

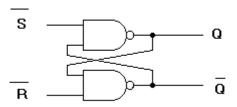

A flip-flop circuit can be constructed from two NAND gates or two NOR gates. These flip-flops are shown in Figure 2 and Figure 3. Each flip-flop has two outputs, Q and Q', and two inputs, set and reset. This type of flip-flop is referred to as an SR flip-flop or SR latch.

By assuming previous values Q=1 and  $\overline{Q}$ =0, for S=0 and R=0 there is no change in the output. The flip-flop in Fig1 has two useful states. When Q=1 and  $\overline{Q}$ =0, it is in the *set state* (or 1-state). When Q=0 and  $\overline{Q}$ =1, it is in the *clear state* (or 0-state).

The outputs Q and  $\overline{Q}$  are complements of each other and are referred to as the normal and complement outputs, respectively. The binary state of the flip-flop is taken to be the value of the normal output. When a 1 is applied to both the set(S) and reset (R) inputs of the flip-flop in Fig1, both Q and  $\overline{Q}$  outputs go to 0. This condition violates the fact that both outputs are complements of each other. In normal operation this condition must be avoided by making sure that 1's are not applied to both inputs simultaneously.

(a) Logic diagram

| S | R | $Q_{n+1}$ | $\bar{Q}_{n+1}$  | Status    |

|---|---|-----------|------------------|-----------|

| 0 | 0 | $Q_n$     | $\overline{Q}_n$ | No change |

| 0 | 1 | 0         | 1                | Reset     |

| 1 | 0 | 1         | 0                | Set       |

| 1 | 1 | 0         | 0                | Invalid   |

(b) Truth table

Figure 2. Basic flip-flop circuit with NOR gates

(a) Logic diagram

| R | s | $Q_{n+1}$ | $\bar{Q}_{n+1}$  | Status    |

|---|---|-----------|------------------|-----------|

| 1 | 1 | $Q_n$     | $\overline{Q}_n$ | No change |

| 1 | 0 | 1         | 0                | Set       |

| 0 | 1 | 0         | 1                | Reset     |

| 0 | 0 | 1         | 1                | Forbidden |

(b) Truth table

Figure 3. Basic flip-flop circuit with NAND gates

The NAND basic flip-flop circuit in figure 3 operates with inputs normally at 1 unless the state of the flip-flop has to be changed. A 0 applied momentarily to the set input causes Q to go to 1 and  $\overline{Q}$  to go to 0, putting the flip-flop in the set state. When both inputs go to 0, both outputs go to 1. This condition should be avoided in normal operation.

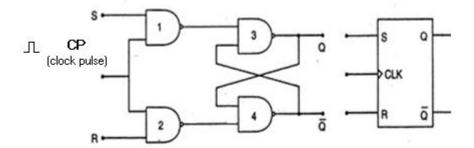

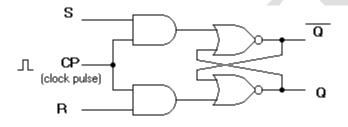

## Introduction - Clocked SR Flip-Flop using NAND gate

(a) Logic diagram

b) symbol of SR FF

| СР    | S | R | $Q_{n+1}$ | $\bar{Q}_{n+1}$    | Status    |

|-------|---|---|-----------|--------------------|-----------|

| Т     | 0 | 0 | $Q_n$     | $\overline{Q}_{n}$ | No change |

| Т     | 0 | 1 | 0         | 1                  | Reset     |

| Т     | 1 | 0 | 1         | 0                  | Set       |

| T     | 1 | 1 | 0         | 0                  | Invalid   |

| NO CP | X | X | $Q_n$     | $\overline{Q}_n$   | No change |

(c) Truth table

Figure 4. Basic flip-flop circuit with NAND gates and clock pulses

Here the inputs are S and R. the circuit consists of two NAND gates and two NAND inverters. The two NAND gates cross connected as shown in figure 4.

Case1: If S=R=0, and CP=1 the output does not change i.e. it remains with the pervious state values. As shown in row 2 of the truth table.

Case2: If S=0, R=1, and CP=1 then output Q becomes 0 and is shown in row 3 of the truth table. This state is called RESET state.

Case3: If S=1, R=0, and CP=1 then output Q becomes 1 and is shown in row 4 of the truth table. This state is called SET state.

Case4: If S=1, R=1, and CP=1 then output Q becomes  $0 \overline{Q}$  also become 0 and is shown in row 5 of the truth table. This state is called Invalid state. This is state should be avoided.

## **Clocked SR Flip-Flop**

The figure 5 shows the clocked SR flip-flop. It consists of a basic NOR flip-flop and two AND gates. The outputs of the two AND gates remain at 0 as long as the clock pulse (or CP) is 0, regardless of the S and R input values.

When the clock pulse goes to 1, information from the S and R inputs passes through to the basic flip-flop. With both S=1 and R=1, the occurrence of a clock pulse causes both outputs to momentarily go to 0.

When the pulse is removed, the state of the flip-flop is indeterminate, i.e., either state may result, depending on whether the set or reset input of the flip-flop remains a 1 longer than the transition to 0 at the end of the pulse.

(a) Logic diagram

| СР    | S | R | $Q_{n+1}$ | $\bar{Q}_{n+1}$    | Status    |

|-------|---|---|-----------|--------------------|-----------|

| Л     | 0 | 0 | $Q_n$     | $\overline{Q}_{n}$ | No change |

| Л     | 0 | 1 | 0         | 1                  | Reset     |

| Л     | 1 | 0 | 1         | 0                  | Set       |

| Л     | 1 | 1 | 0         | 0                  | Invalid   |

| NO CP | X | X | $Q_n$     | $\overline{Q}_{n}$ | No change |

(b) Truth table

Figure 5 Clocked SR flip-flop

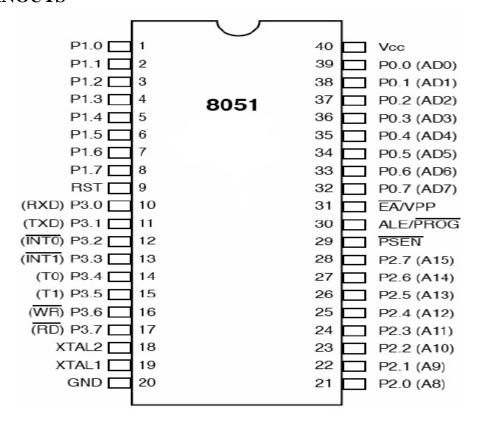

### Microcontroller 8051

A micro controller is an integrated circuit or a chip with a processor and other support devices like program memory, data memory, I/O ports, serial communication interface etc integrated together. Unlike a microprocessor (ex: Intel 8085), a microcontroller does not require any external interfacing of support devices. We all know that 8051 is an 8-bit microcontroller. Here is the pin out diagram for the 8051 is shown is figure 6. The features of 8051 are listed below.

### Features of 8051Microcontroller

- 4KB ROM

- 128 bytes internal RAM

- 4 register banks of 8 bytes each (R0-R7)

- 16 bytes of bit-addressable area

- 80 bytes of general purpose memory

- Four 8-bit I/O ports (P0-P3)

- Two 16-bit timers (Timer0 & Timer1)

- One serial receiver-transmitter interface

- Five interrupt sources (2 external & 3 internal)

- One oscillator (generates clock signal)

### **8051 PINOUTS**

Figure 6. 40 pins 8051 MICROCONTROLLER

The microcontroller pin details is discussed below. It has

- 4 input/output ports (each 8 bits or 1 byte)

- Except Port1, each port has some dual nature or functionality

- RXD/TXD for serial transmission

- Interrupts and Timers

The remaining PINS are just for powering up the device. There are four ports as **P0**, **P1**, **P2** and **P3**. And they all have 8 pins for data transfer so the individual pins are named as **P0.0-P0.7**, **P1.0-P1.7**, **P2.0-P2.7**, and **P3.0 - P3.7**.

As mentioned above, control signals are used for external memory interfacing. If there is no requirement of external memory interfacing then, EA pin is pulled high (connected to Vcc) and two others PSEN and ALE are left alone.

We can also use a 0.1 micro farad decoupling capacitor connected to Vcc, it is used to avoid High Frequency oscillations at input.

There are four ports numbered 0,1,2,3 and called as Port 0, Port 1, Port 2 and Port 3 which are used for external interfacing of devices like DAC, ADC, 7 segment display, LED etc. Each port has 8 I/O lines and they all are bit programmable.

For describing pin diagram and pin configuration of 8051, we are taking into consideration a 40 pin DIP (Dual inline package).

### Pins configuration in detail:

**Pin-40 :** Named as **Vcc** is the main power source. Usually it is +5V DC.

**Pins 32-39:** Known as **Port 0** (**P0.0 to P0.7**) – In addition to serving as I/O port, lower order address and data bus signals are multiplexed with this port (to serve the purpose of external memory interfacing). This is a bi directional I/O port (the only one in 8051) and external pull up resistors are required to function this port as I/O.

**Pin-31:- ALE** Address Latch Enable is used to de-multiplex the address-data signal of port 0 (for external memory interfacing.) 2 ALE pulses are available for each machine cycle.

**Pin-30:- EA** External Access input is used to enable or disallow external memory interfacing. If there is no external memory requirement, this pin is pulled high by connecting it to Vcc.

**Pin- 29:- PSEN** or Program Store Enable is used to read signal from external program memory.

**Port 2 (P 2.0 to P 2.7) Pins- 21-28:-** Known as Port 2 (P 2.0 to P 2.7) – in addition to serving as I/O port, higher order address bus signals are multiplexed with this quasi bi directional port.

**Pin 20:-** Named as **GND**– it represents ground (0 V) connection.

**Pin 18 and 19 XTAL1 and XTAL2:** Internal oscillator input and output. A quartz crystal which specifies operating frequency is usually connected to these pins. Instead of it, miniature ceramics resonators can also be used for frequency stability. Later versions of microcontrollers operate at a frequency of 0 Hz up to over 50 Hz.

**Pins 10 – 17:-** Known as **Port 3**. This port also serves some other functions like interrupts, timer input, control signals for external memory interfacing RD and WR, serial communication signals RxD and TxD etc. This is a quasi bi directional port with internal pull up.

**Pins 10** – **17:-** Similar to port 1, each of these pins can serve as general input or output. Besides, all of them have alternative functions:

Pin 10 RXD: Serial asynchronous communication input or Serial synchronous communication output.

Pin 11 TXD Serial asynchronous communication output or Serial synchronous communication clock output.

Pin 12 INTO Interrupt 0 input.

**PIN 13 INT1:** Interrupt 1 input.

Pin 14 T0 Counter 0 clock input.

Pin 15 T1: Counter 1 clock input.

**Pin 16 WR:** Write to external (additional) RAM.

Pin 17 RD Read from external RAM.

**Pin 9:-** As explained before **RESET** pin is used to set the 8051 microcontroller to its initial values, while the microcontroller is working or at the initial start of application. The RESET pin must be set high for 2 machine cycles.

**Pins 1 – 8:-** Known **as Port 1**. Unlike other ports, this port does not serve any other functions. Port 1 is an internally pulled up, quasi bi directional I/O port.

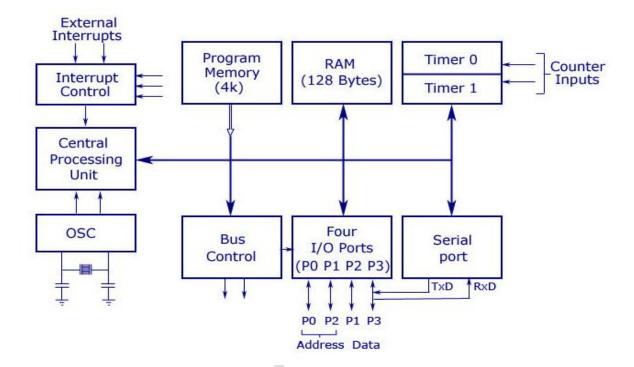

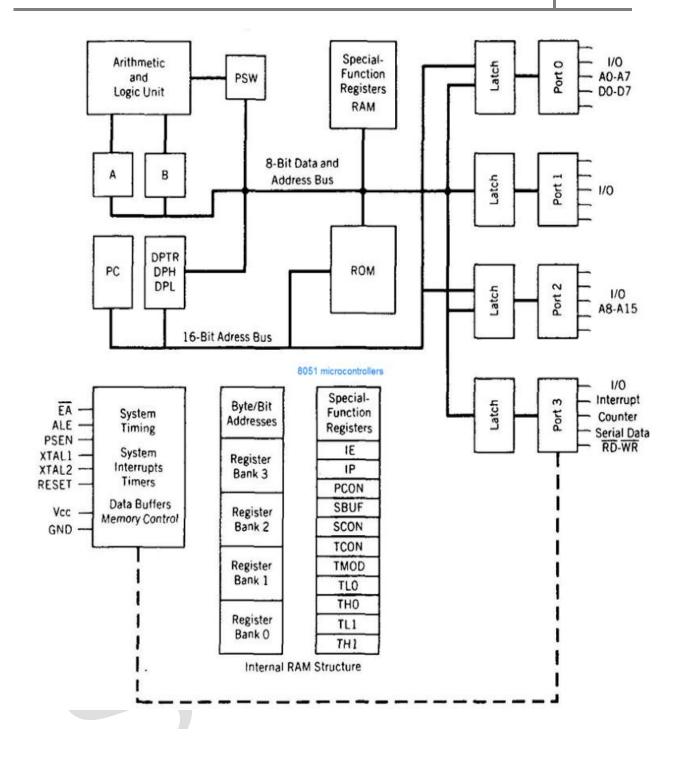

### 8051 Internal Architecture

The figure 7 shows the Internal block diagram of 8051 microcontroller.

### 1. 8051 has eight-Bit CPU with register A and B.

It consists of 8-bit ALU (Arithmetic logical unit) it has 8-bit registers namely A (accumulator) and B (arithmetic) registers. The 8051 has 34 general purpose registers. The 8 bit register PSW is explained below.

### 2. Program Status Word (PSW) Register

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| CY   | AC   | F0   | RS1  | RS0  | OV   |      | P    |

**PSW register** is one of the most important Special Function Registers. It contains several status bits that reflect the current state of the CPU. Besides, this register contains Carry bit, Auxiliary Carry, two register bank select bits, Overflow flag, parity bit and user-definable status flag.

Figure 7. Internal Block diagram of the 8051 microcontroller

- **P Parity bit.** If a number stored in the accumulator is even then this bit will be automatically set (1), otherwise it will be cleared (0). It is mainly used during data transmit and receive via serial communication.

- --- Bit 1. This bit is intended to be used in the future versions of microcontrollers.

- **OV Overflow** occurs when the result of an arithmetical operation is larger than 255 and cannot be stored in one register. Overflow condition causes the OV bit to be set (1). Otherwise, it will be cleared (0).

**RS0, RS1 - Register bank select bits.** These two bits are used to select one of four register banks of RAM. By setting and clearing these bits, registers R0-R7 are stored in one of four banks of RAM.

| RS1 | RS0 | RAM Area                 |

|-----|-----|--------------------------|

| 0   | 0   | Register bank 0 selected |

| 0   | 1   | Register bank 1 selected |

| 1   | 0   | Register bank 2 selected |

| 1   | 1   | Register bank 3 selected |

**F0 - Flag 0.** This is a general-purpose bit available for use.

**AC - Auxiliary Carry Flag** is used for BCD operations only.

**CY - Carry Flag** is the (ninth) auxiliary bit used for all arithmetical operations and shift instructions.

### 3. The 8051 has 16 bit Data Pointer Register (DPTR) as shown below.

DPTR register is a data pointer register. It consists of two separate registers: DPH (Data Pointer High) and (Data Pointer Low). For this reason it may be treated as a 16-bit register or as two independent 8-bit registers. Their 16 bits are primarily used for external memory addressing. Besides, the DPTR Register is usually used for storing data and intermediate results.

| Bit (15-8) | Bit(7-0) |

|------------|----------|

| DPH        | DPL      |

|            |          |

**DPTR** register

### 4. The 8 bit wide Stack Pointer (SP) Register is used in 8051 microcontroller.

A value stored in the Stack Pointer points to the first free stack address and permits stack availability. Stack pushes increment the value in the Stack Pointer by 1. Likewise, stack pops decrement its value by 1.

## 5. P0, P1, P2, P3 - Input/Output Registers

If neither external memory nor serial communication system are used then 4 ports within total of 32 input/output pins are available for connection to peripheral environment. Each bit within these ports affects the state and performance of appropriate pin of the microcontroller. Thus, bit logic state is reflected on appropriate pin as a voltage (0 or 5 V) and vice versa, voltage on a pin reflects the state of appropriate port bit.

### 6. Internal RAM and Internal ROM

The 8051 has 4096 Bytes of Internal Bytes of ROM with address 0000H to 0FFFH. The Internal RAM has 128 bytes containing four register banks and each having eight registers R0-R7.

#### 7. Control registers

8051 has following control registers Timer/counter Control (TCON) Register, Timer/counter Mode (TMOD) Register, Serial Port Control (SCON) Register, Serial Buffer (SBUF) Register, IE Register (Interrupt Enable), IP Register (Interrupt Priority).

#### 8. Oscillator and clock

8051 has 12 M Hz oscillator frequency.

### Working of 8051 Microcontroller:

- 1. The central processing unit fetches the program from program memory (ROM), and execute the same.

- 2. The program is a collection of a set of instructions.

- 3. The microcontroller executes the one instruction at a time, after completion it fetches next instruction to execute.

- 4. The data required for ALU is obtained from the data memory (RAM).

- 5. Speed of operations is more, It talks less access time to execute, since both program memory and data memory are within microcontroller.

- 6. The hardware counter/ timers present with in microcontroller, used to set time. And it introduces the delay.

- 7. The serial port is used for serial to parallel conversion and vice-versa.

- 8. The signals from interrupting source are connected to interrupt controller unit of the microcontroller.

- 9. Interrupt service routines are also present with microcontroller.

- 10. The complete working of the microcontroller also depends on how we have written the coding (programming) using instruction.

The detailed architecture of 8051 microcontroller is shown in figure 8.

Figure8. Detailed architecture of 8051

## **Stepper motor**

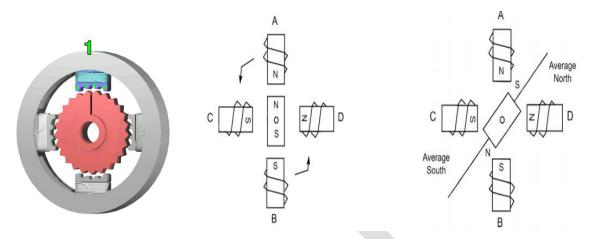

Stepper motor: a device that translates electrical pulses into mechanical movement usually used in robotics Permanent magnet (PM) rotor surrounded by a stator Stepper shaft (rotor) moves in a fixed repeatable increment rather than running freely as in conventional motors.

The stepper motor is used for position control in application such as Disk drives dot matrix printers and Robotics. Stepper motor have a permanent magnet rotor (also called as shaft) surrounded by a stator.

Figure 9. Rotor (stepper shaft) Alignment

### 4 phase steppe motor:

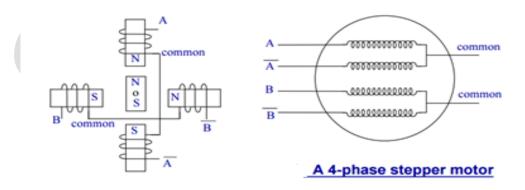

The stepper motors have four stator windings that are paired with a centre-tapped common as shown in figure 10. In figure we have 6 leads: 4 stator windings leads and 2 centre-tapped commons

Figure 10. A 4 phase stepper motor

Step angle: the step angle is the minimum degree of rotation associated with a single step. The smaller of step angle, higher degree of precision I position control.

Stepper motor position control: there are several widely used sequences wher each has a different degree of precision.

Normally 4-step sequence

8step sequence (half stepping)

There are several widely used sequences where each has a different degree of precision. Normal 4-step sequence 8-step sequence (half-stepping) Step angle – the step angle is the minimum degree of rotation associated with a single step. The smaller of step angle, higher degree of precision in position control.

| Motor Step Angle (°) | Steps per Revolution |

|----------------------|----------------------|

| 0.72                 | 500                  |

| 1.8                  | 200                  |

| 2.0                  | 180                  |

| 2.5                  | 144                  |

| 5.0                  | 72                   |

| 7.5                  | 48                   |

## Normal 4-Step Sequence

|   | Clockwise |   |

|---|-----------|---|

| 7 | \<br>\    | 7 |

| Step# | Winding A | Winding B | Winding A | Winding B |

|-------|-----------|-----------|-----------|-----------|

| 1     | 1         | 0         | 0         | 1         |

| 2     | 1         | 1         | 0         | 0         |

| 3     | 0         | 1         | 1         | 0         |

| 4     | 0         | 0         | 1         | 1         |

# 8-Step Sequence (Half Step)

| Step # | Winding A | Winding B | Winding A | Winding B |

|--------|-----------|-----------|-----------|-----------|

| 1      | 1         | 0         | 0         | 1         |

| 2      | 1         | 0         | 0         | 0         |

| 3      | 1         | 1         | 0         | 0         |

| 4      | 0         | 1         | 0         | 0         |

| 5      | 0         | 1         | 1         | 0         |

| 6      | 0         | 0         | 1         | 0         |

| 7      | 0         | 0         | 1         | 1         |

| 8      | 0         | 0         | 0         | 1         |

There is many number of stepper motor available in market. We can buy any of them as per our requirement.

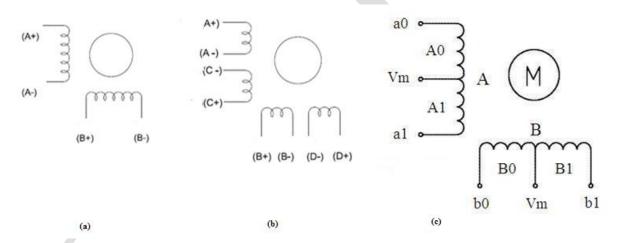

According to the no. of terminals outcomes from stepper motor, one can decide type of motor. Generally types of stepper motor are...

- Unipolar,

- Bipolar and

- Universal Motor

### **Unipolar stepper motor:**

Unipolar stepper motor has mainly 6 terminals, a universal stepper motor has eight, and while bipolar has only 4 terminals. Unipolar stepper motor has mainly two coils. Coils are generally similar type but both is not connected each other. There is common terminal at center of each coil. One can identify two separate coils by join together.

**Figure 11.** Common stepper motor types (a). Bipolar stepper motor (b). Universal stepper motor (c) Unipolar stepper motor

### **Bipolar stepper motor:**

In bipolar stepper motor there are generally 4 terminals. The universal stepper motor can be configured for all three modes, while the unipolar can be either unipolar or bipolar. Obviously the bipolar cannot be configured for unipolar nor universal.

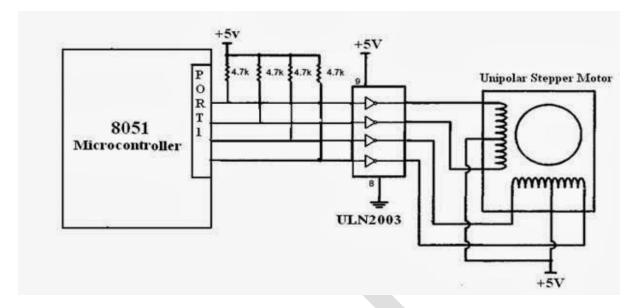

### **Interfacing stepper motor to 8051 microcontroller**

The stepper motor is interfaced to 8051 microcontroller as shown in figure 12. The four leads of the stator windings are controlled by four bits of the 8051 port1 (port 1.0 to port1.3). However, since the 8051 lacks sufficient current to drive the stepper motor windings, we use a driver such as the ULN 2003 to energize the stator. Instead of ULN 2003, Transistors can also be as drivers.

However, if transistors are used as drivers, we must also use diodes to take care of inductive current generated when the coil is turned off. One reason that using the ULN 2003 is preferable to use of transistors as drivers is that the ULN 2003 has an internal diode to take care of back emf. Two COM ports of unipolar stepper motor is connected to +5V supply.

Figure 12. 8051 connection to stepper motor

### **References:**

- 1. D.P. Kothari, I. J. Nagrath, "Basic Electronics", McGraw Hill Education (India) Private Limited, 2014.

- 2. MuhammadAli Mazidi, "The 8051 Microcontroller and Embedded. Systems. Using Assembly and C." Second Edition, 2011, Pearson India.